#### **Issues in High-Level Connectivity Synthesis**

Barry M. Pangrle\*, Forrest D. Brewer\*\*, Donald A. Lobo\*, and Andrew Seawright\*\*

\*CS Dept. Pennsylvania State University, University Park PA, 16802

\*\*ECE Dept. University of California, Santa Barbara CA, 93106

This research supported in part by NSF Grant MIP 88-09250, and the University of California MICRO program, 1990

Chip HDL { while(~b)

ECE Dept. University of California, Santa Barbara CS Dept. Pennsylvania State University

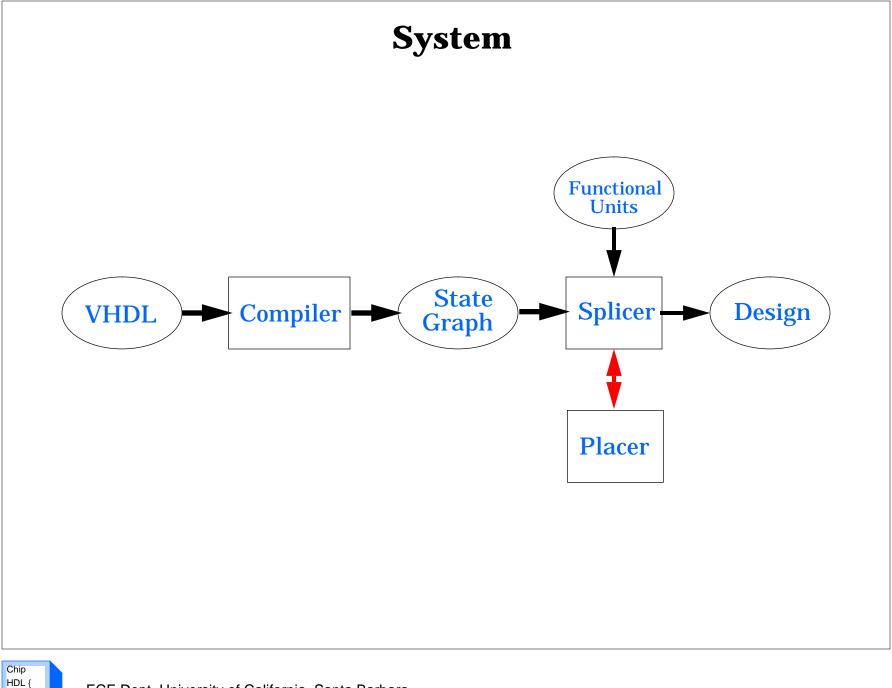

# Introduction

- Concurrent Interconnection Synthesis and 1-D Layout Generation

- Multiplexer/Bus Trade-Offs

- Busses, Registers, and Tracks

# **Related Work**

- Hercules, ELF, HAL, LYRA, MAHA, Facet

- PARBUS, CATHEDERAL-II, SPAID, SYCO, BUD

ECE Dept. University of California, Santa Barbara CS Dept. Pennsylvania State University

while(~b)

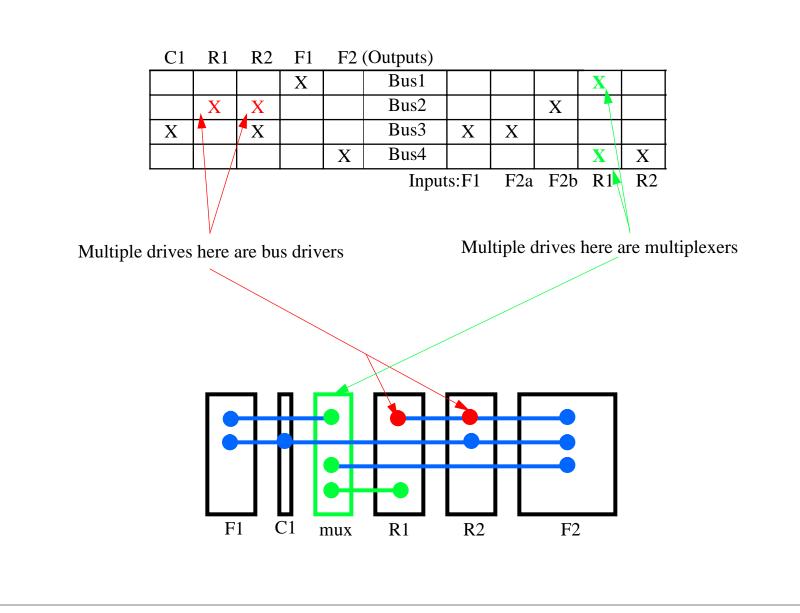

#### **Model and Constraints For these Experiments**

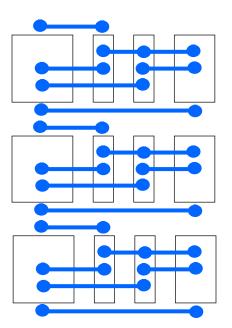

- I-D Bit-Sliced Placement Model

- Track Minimization Primary Objective

- Sized Cells

- Busses Used Once per Clock Cycle

- Unidirectional Data Transfers

- Cell Inputs are Not Latched

- Minimum Register Designs

# **Connectivity to Layout Mapping**

Chip HDL { while(~b)

ECE Dept. University of California, Santa Barbara CS Dept. Pennsylvania State University

#### **Busses, Registers, and Tracks**

- Number of Tracks Needed In a Design is not Equivalent to Number of Busses

- More Than the Minimal Number of Registers In a Design Can Save Tracks

- What Is The Maximum Number of Tracks <u>Necessary</u> In a Design, If the Number of Registers is not Minimized?

Lemma:

An Upper Bound is Number of Simultaneously Active Functional Unit Outputs Plus 2\*

\*binary operations

Chip HDL { while(~b)

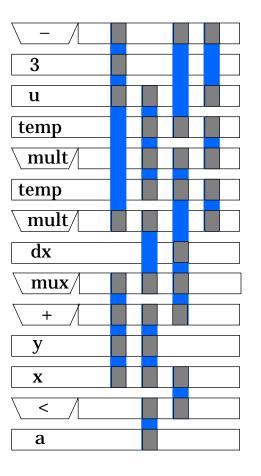

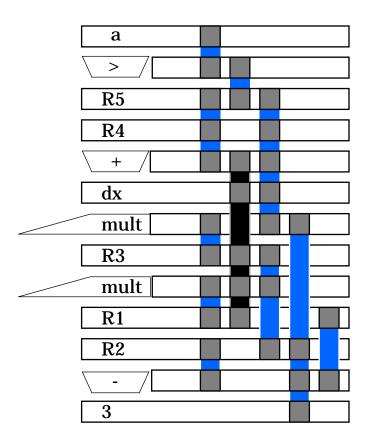

#### **HAL Example**

- Sized Cells

- 4 tracks, wirelength = 1577

Chip HDL { while(~b)

ECE Dept. University of California, Santa Barbara CS Dept. Pennsylvania State University

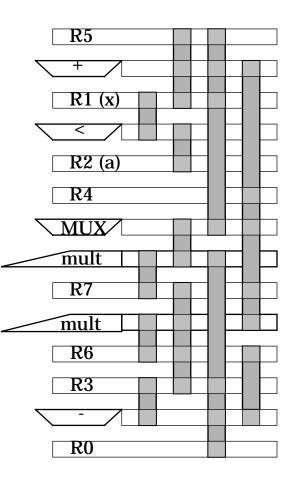

# **Elliptic Filter**

- 1 multiply, 1 adder (4 clock multiply)

- Sized Cells

- 5 tracks, wirelength 3326 (26cpu sec.)

|            | <br> |   |  |

|------------|------|---|--|

| temp       |      |   |  |

| t33        |      |   |  |

| t13        |      |   |  |

| t2         |      |   |  |

| <u>mux</u> |      |   |  |

| t39        |      |   |  |

| +          |      |   |  |

| <u>mux</u> |      |   |  |

| temp       |      |   |  |

| i          |      |   |  |

| t38        |      |   |  |

| temp       |      |   |  |

| t18        |      |   |  |

| t26        |      |   |  |

| mult       |      | ] |  |

| ROM        |      |   |  |

Chip HDL { while(~b)

## Results

| <u>Sample</u> | <u>Tracks</u> | <u>Wirelength</u> | <u>Busses</u> | <u>D.P. Mux</u> | <u>Muxinputs</u> |

|---------------|---------------|-------------------|---------------|-----------------|------------------|

| Hal           | 4             | 33                | 12            | 1               | 11               |

| PHal*         | 5             | 27                | 3(7)          | 1               | 10               |

| SHal**        | 5             | 31                | 10            | 3               | 9                |

| Ellip         | 5             | 3326              | 7             | 2               | 26               |

| Hal           | 4             | 1577              | 12            | 1               | 11               |

|               |               |                   |               |                 |                  |

| <u>Example</u> | <u>Tracks</u> | Load Balanced |

|----------------|---------------|---------------|

| DE1            | 4             | Yes           |

| DE2            | 4             | Yes           |

| DE3            | 5             | Yes           |

| DE4            | 4             | No            |

| DE5            | 5             | No            |

| DE6            | 4             | No            |

| AFB            | 6min          | Yes           |

| AFU            | 5min          | No            |

ECE Dept. University of California, Santa Barbara CS Dept. Pennsylvania State University

# Conclusions

- Number of Busses is Poor Estimate of Number of Tracks

- Use Caution in Minimizing Number of Busses in Scheduler

- Designs with More than Minimal Number of Registers Can Win

- In 1-D Layout, Load Balanced Schedules May Not Be Track Efficient

Chip HDL { while(~b)

ECE Dept. University of California, Santa Barbara CS Dept. Pennsylvania State University